# Deep SLAM Study

July 11, 2018 Dong-Won Shin

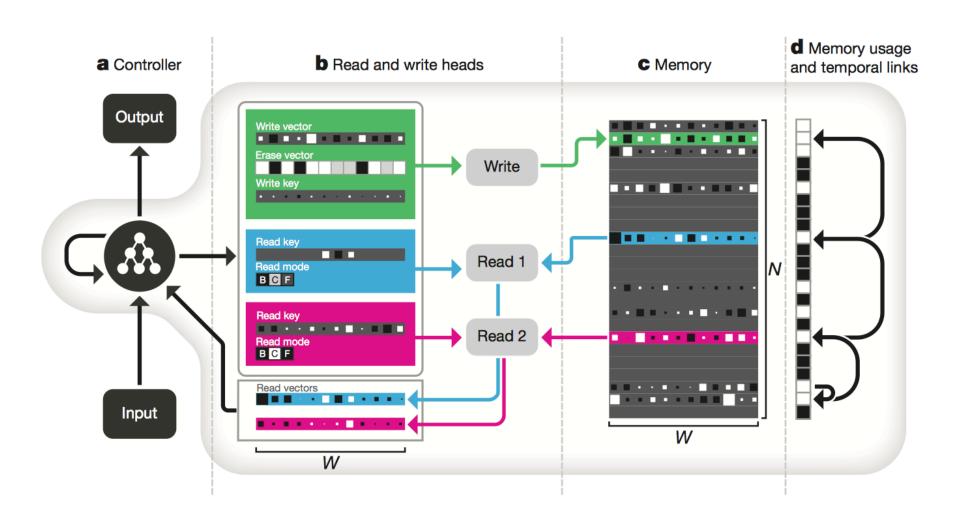

### **DNC** architecture

Differentiable attention mechanisms

### Controller Network

Basically, the controller network is deep LSTM architecture.

Input gate

$$\mathbf{i}_t^l = \sigma(W_{\mathbf{i}}^l[\boldsymbol{\chi}_t; \boldsymbol{h}_{t-1}^l; \boldsymbol{h}_t^{l-1}] + \boldsymbol{b}_{\mathbf{i}}^l)$$

Forget gate  $f_t^l = \sigma(W_f^l[\boldsymbol{\chi}_t; \boldsymbol{h}_{t-1}^l; \boldsymbol{h}_t^{l-1}] + \boldsymbol{b}_f^l)$

State (long-term memory)  $\mathbf{s}_t^l = f_t^l \mathbf{s}_{t-1}^l + \mathbf{i}_t^l \mathrm{tanh}(W_{\mathbf{s}}^l[\boldsymbol{\chi}_t; \boldsymbol{h}_{t-1}^l; \boldsymbol{h}_t^{l-1}] + \boldsymbol{b}_s^l)$

Output gate  $\mathbf{o}_t^l = \sigma(W_{\mathbf{o}}^l[\boldsymbol{\chi}_t; \boldsymbol{h}_{t-1}^l; \boldsymbol{h}_t^{l-1}] + \boldsymbol{b}_{\mathbf{o}}^l)$

Hidden (short-term memory)  $\mathbf{h}_t^l = \mathbf{o}_t^l \mathrm{tanh}(\mathbf{s}_t^l)$

Read vector  $r_{t-1}^1, ..., r_{t-1}^R$  from read heads at the previous time step

Interface vector

$$\boldsymbol{\xi}_t = W_{\boldsymbol{\xi}}[\boldsymbol{h}_t^1; \dots; \boldsymbol{h}_t^L]$$

Output vector  $\boldsymbol{y}_t = \boldsymbol{v}_t + W_{\mathrm{r}}[\boldsymbol{r}_t^1; \dots; \boldsymbol{r}_t^R]$ , where  $\boldsymbol{v}_t = W_{\boldsymbol{y}}[\boldsymbol{h}_t^1; \dots; \boldsymbol{h}_t^L]$

### Interface Vector

Interface parameters

$$\boldsymbol{\xi}_t \!=\! \left[\boldsymbol{k}_t^{\mathrm{r},1}; \ldots; \boldsymbol{k}_t^{\mathrm{r},R}; \hat{\boldsymbol{\beta}}_t^{\mathrm{r},1}; \ldots; \hat{\boldsymbol{\beta}}_t^{\mathrm{r},R}; \boldsymbol{k}_t^{\mathrm{w}}; \hat{\boldsymbol{\beta}}_t^{\mathrm{w}}; \boldsymbol{\hat{e}}_t; \boldsymbol{v}_t; \hat{\boldsymbol{f}}_t^1; \ldots; \hat{\boldsymbol{f}}_t^R; \hat{\boldsymbol{g}}_t^{\mathrm{a}}; \hat{\boldsymbol{g}}_t^{\mathrm{w}}; \hat{\boldsymbol{\sigma}}_t^1; \ldots; \hat{\boldsymbol{\pi}}_t^R\right]$$

- $R \text{ read keys } \{ \boldsymbol{k}_t^{\mathrm{r},i} \in \mathbb{R}^W; 1 \leq i \leq R \};$

- R read strengths  $\{\beta_t^{\mathbf{r},i} = \text{oneplus}(\hat{\beta}_t^{\mathbf{r},i}) \in [1,\infty); 1 \le i \le R\};$

- the write key  $\mathbf{k}_t^{\mathrm{w}} \in \mathbb{R}^W$ ;

- the write strength  $\beta_t^{\text{w}} = \text{oneplus}(\hat{\beta}_t^{\text{w}}) \in [1,\infty);$

- the erase vector  $\mathbf{e}_t = \sigma(\mathbf{\hat{e}}_t) \in [0,1]^W$ ;

- the write vector  $\mathbf{v}_t \in \mathbb{R}^W$ ;

- R free gates  $\{f_t^i = \sigma(\hat{f}_t^i) \in [0,1]; 1 \le i \le R\};$

- the allocation gate  $g_t^a = \sigma(\hat{g}_t^a) \in [0,1]$ ;

- the write gate  $g_t^{\mathbf{w}} = \sigma(\hat{g}_t^{\mathbf{w}}) \in [0,1]$ ; and

- $R \text{ read modes } \{\boldsymbol{\pi}_t^i = \operatorname{softmax}(\boldsymbol{\hat{\pi}}_t^i) \in \mathcal{S}_3; 1 \leq i \leq R\}.$

# Reading and Writing to Memory

Read operation

$$oldsymbol{r}_t^i = \underline{M}_t^{ op} \underline{oldsymbol{w}_t^{ ext{r},i}}$$

memory read weight

Write operation

$$M_t = M_{t-1} \circ (E - oldsymbol{w}_t^{\mathrm{w}} oldsymbol{e}_t^{ op}) + oldsymbol{w}_t^{\mathrm{w}} oldsymbol{v}_t^{ op}$$

erasing writing

- the erase vector  $\mathbf{e}_t = \sigma(\mathbf{\hat{e}}_t) \in [0,1]^W$ ;

- the write vector  $\mathbf{v}_t \in \mathbb{R}^W$ ;

- To determine where to write

- Combination of <u>content-based addressing</u> and <u>dynamic memory allocation</u>

- To determine where to read

- Combination of <u>content-based addressing</u> and <u>temporal memory linkage</u>

- Content-based addressing

$$\mathcal{C}(M, k, \beta)[i] = \frac{\exp\{\mathcal{D}(k, M[i, \cdot])\beta\}}{\sum_{j} \exp\{\mathcal{D}(k, M[j, \cdot])\beta\}} \text{ ,where } \mathcal{D}(u, v) = \frac{u \cdot v}{|u||v|}$$

Lookup key Key strength

- $R \text{ read keys } \{\boldsymbol{k}_t^{\mathrm{r},i} \in \mathbb{R}^W; 1 \leq i \leq R\};$

- $R \text{ read strengths } \{\beta_t^{r,i} = \text{oneplus}(\hat{\beta}_t^{r,i}) \in [1,\infty); 1 \le i \le R\};$

- the write key  $\mathbf{k}_t^{\mathrm{w}} \in \mathbb{R}^W$ ;

- the write strength  $\beta_t^{\text{w}} = \text{oneplus}(\hat{\beta}_t^{\text{w}}) \in [1,\infty);$

- Dynamic memory allocation

- · To allow the controller to free and allocate memory as needed

- Retention vector: how much each location will not be freed by the free gates

$$\boldsymbol{\psi}_{t} = \prod_{i=1}^{R} \left( \mathbf{1} - \boldsymbol{f}_{t}^{i} \mathbf{w}_{t-1}^{r,i} \right)$$

Usage vector: which locations have been used so far

$$\boldsymbol{u}_{t} = (\boldsymbol{u}_{t-1} + \boldsymbol{w}_{t-1}^{w} - \boldsymbol{u}_{t-1} \circ \boldsymbol{w}_{t-1}^{w}) \circ \boldsymbol{\psi}_{t}$$

Allocation weighting: to provide new locations for writing

$$a_t[\phi_t[j]] = (1 - u_t[\phi_t[j]]) \prod_{i=1}^{j-1} u_t[\phi_t[i]]$$

Content weighting: from content-based addressing

$$\boldsymbol{c}_{t}^{\mathrm{w}} = \mathcal{C}(M_{t-1}, \boldsymbol{k}_{t}^{\mathrm{w}}, \boldsymbol{\beta}_{t}^{\mathrm{w}})$$

Write weighting

$$\boldsymbol{w}_{t}^{\mathrm{w}} = \boldsymbol{g}_{t}^{\mathrm{w}} [\boldsymbol{g}_{t}^{\mathrm{a}} \boldsymbol{a}_{t} + (1 - \boldsymbol{g}_{t}^{\mathrm{a}}) \boldsymbol{c}_{t}^{\mathrm{w}}]$$

- R free gates  $\{f_t^i = \sigma(\hat{f}_t^i) \in [0,1]; 1 \le i \le R\}$ ;

- the allocation gate  $g_t^a = \sigma(\hat{g}_t^a) \in [0,1]$ ;

- the write gate  $g_t^{\text{w}} = \sigma(\hat{g}_t^{\text{w}}) \in [0,1]$ ; and

- Temporal memory linkage

- To keep track of consecutively modified memory locations

- Precedence weighting

- $p_t[i]$ : the degree to which location i was the last one written to

$$egin{aligned} oldsymbol{p}_0 &= oldsymbol{0} \\ oldsymbol{p}_t &= egin{pmatrix} 1 - \sum_i oldsymbol{w}_t^{\mathrm{w}}[i] \end{pmatrix} oldsymbol{p}_{t-1} + oldsymbol{w}_t^{\mathrm{w}} \end{aligned}$$

- Link matrix

- $L_t[i,j]$ : the degree to which location i was the location written to after location j

$$egin{aligned} L_0[i,j] = 0 & orall i,j \ L_t[i,i] = 0 & orall i \ L_t[i,j] = (1-oldsymbol{w}_t^{\mathrm{w}}[i]-oldsymbol{w}_t^{\mathrm{w}}[j])L_{t-1}[i,j] + oldsymbol{w}_t^{\mathrm{w}}[i]oldsymbol{p}_{t-1}[j] \end{aligned}$$

Forward and backward weighting

$$oldsymbol{f}_t^i = L_t oldsymbol{w}_{t-1}^{\mathrm{r},i} \ oldsymbol{b}_t^i = L_t^ op oldsymbol{w}_{t-1}^{\mathrm{r},i}$$

- Temporal memory linkage

- Content weighting: from content-based addressing

$$\boldsymbol{c}_t^{\mathrm{r},i} = \mathcal{C}(M_t, \boldsymbol{k}_t^{\mathrm{r},i}, \beta_t^{\mathrm{r},i})$$

Read weighting

$$\mathbf{w}_{t}^{\mathrm{r},i} = \mathbf{\pi}_{t}^{i}[1]\mathbf{b}_{t}^{i} + \mathbf{\pi}_{t}^{i}[2]\mathbf{c}_{t}^{\mathrm{r},i} + \mathbf{\pi}_{t}^{i}[3]\mathbf{f}_{t}^{i}$$

- $R \text{ read modes } \{\boldsymbol{\pi}_t^i = \text{softmax}(\boldsymbol{\hat{\pi}}_t^i) \in \mathcal{S}_3; 1 \leq i \leq R\}.$

- R read keys { $\mathbf{k}_t^{\mathrm{r},i} \in \mathbb{R}^W$ ;  $1 \le i \le R$ };

- R read strengths  $\{\beta_t^{r,i} = \text{oneplus}(\hat{\beta}_t^{r,i}) \in [1,\infty); 1 \le i \le R\};$

- the write key  $\mathbf{k}_t^{\mathrm{w}} \in \mathbb{R}^W$ ;

- the write strength  $\beta_t^{\text{w}} = \text{oneplus}(\hat{\beta}_t^{\text{w}}) \in [1,\infty);$

# Thank you